Конфігуровані логічні блоки

Незалежно від різних виробників і кілька різних архітектур і наборів функцій, більшість FPGA має загальний підхід. Основними компонентними блоками будь FPGA є гнучкий програмований «логічний блок» (CLB), оточений програмованими «блоками введення / виведення» з ієрархією маршрутизації каналів, що з’єднують різні блоки на платі.

Крім того, вони можуть складатися з DLL-бібліотек для розподілу і управління годинами і пам’яті RAM виділеного блоку з основним будівельним блоком логічної осередком. Остання складається з генератора вхідних функцій, логіки перенесення і зберігання елементів. Генератори реалізуються у вигляді довідкових таблиць і залежать від введення. Наприклад, Xilinx Spartan II має 4 вхідних LUT із забезпеченням кожного 16X1 бітним синхронним ОЗП з використанням мультиплексорів як регістрів зсуву для захоплення даних в пакетному режимі. Елементи зберігання є чутливими до країв тригерів або до рівня засувок.

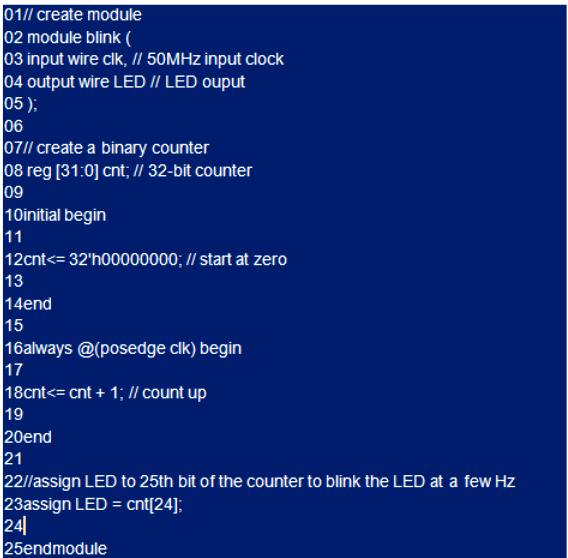

Фрагмент програмування ПЛИСов:

Базовий блок вводу / виводу показаний нижче.

Буфера у вхідних і вихідних шляхах надсилають сигнали у внутрішню логіку і підсумкові майданчика безпосередньо або через тригер. Вони налаштовуються на відповідність різним підтримуваних стандартів сигналізації, які можуть бути визначені користувачем і встановлені ззовні.