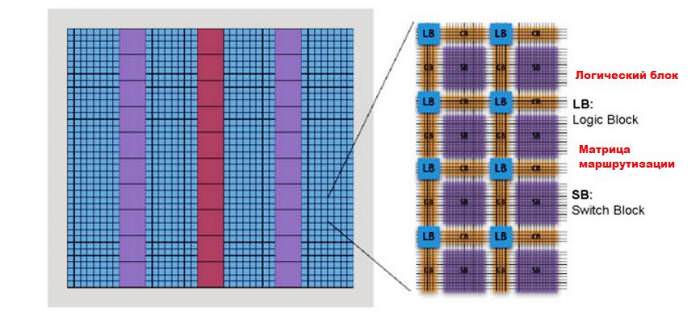

Мікропроцесор складається з декількох блоків, з’єднаних між собою, кожен з них виконує певну функцію. Проект і взаємозв’язок цих блоків називається архітектурою. Швидкість, з якою комп’ютер може читати інструкції і виконувати відповідні обчислення, визначається робочою частотою мікропроцесора. Виробники домоглися великих успіхів у розробці архітектури, що дозволяє комп’ютерам все менше залежати від частоти, тобто мікро з низькими частотами і швидкостями можуть виконувати більше обчислень і завдань. В процесі еволюції архітектури мікропроцесора вона перетворилася з одноядерної в многоядерную, здатну обробляти кілька частин інформації одночасно.

Історія поколінь мікропроцесора

Компанія Fairchild Semiconductor (Ярмарок дитячих напівпровідників), заснована в 1957 році винайшла свою першу інтегральну схему в 1959 році, яка ознаменувала початок історії мікропроцесорів. У 1968 році Гордон Мур, Роберт Нойс і Ендрю Гроув пішли з Ярмарку дитячих напівпровідників і заснували власну компанію: Integrated Electronics (Intel). В 1971 році компанія винайшла перший Intel 4004.

Сьогодні існує кілька поколінь архітектури мікропроцесорів:

- 1-е покоління з 1971 по 1973 роки. У 1971 році INTEL 4004 з тактовою частотою 108 кГц. Протягом цього періоду використовувалися інші моделі на ринку, включаючи Rockwell International PPS-4, INTEL-8008 і National semiconductors IMP-16, вони були не TTL-сумісними пристроями.

- 2-е покоління з 1973 по 1978 рік, реалізовані дуже ефективні 8-розрядні мікропроцесори, такі як Motorola 6800 і 6801, INTEL-8085 і Zilogs-Z80. Внаслідок їх надшвидкої швидкості вони були дорогими, оскільки грунтувалися на виготовленні технології NMOS, тим не менш, незважаючи на ціну, були дуже популярні.

- 3-е покоління архітектури мікропроцесора використовувалося з 1979 по 1980 рік.У цьому періоді були розроблені INTEL 8086/80186/80286 і Motorola 68000 і 68010. Швидкості цих процесорів були в чотири рази краще, ніж у попередників.

- 4-е покоління з 1981 по 1995 роки – були розроблені 32-розрядні мікропроцесори з використанням HCMOS. INTEL-80386 і Motorola 68020/68030 були популярними процесорами.

- 5-е покоління стартувала в 1995 році і по теперішній час. У цьому періоді на ринок випустили 64-розрядну архітектуру сучасного мікропроцесора, до яких відносяться Pentium, Celeron, Dual і Quad Core.